Return loss specification of PCIe Gen4 transmitter and measured return... | Download Scientific Diagram

High Speed High Frequency PCIE 16X PCI Express Riser Extender Card Adapter Cable Cords 22cm | Lazada

TBS 6909-x DVB-S2 PCIE frequency demodulation card HD digital TV receiving card collection network card

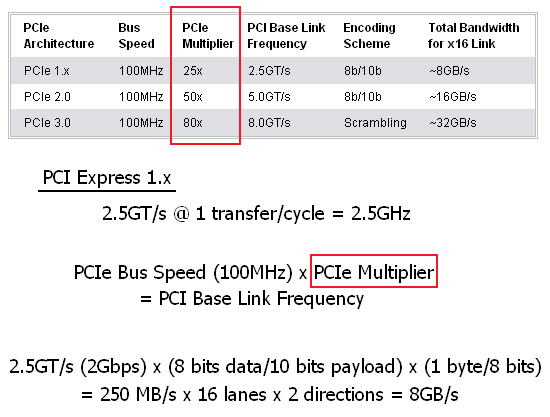

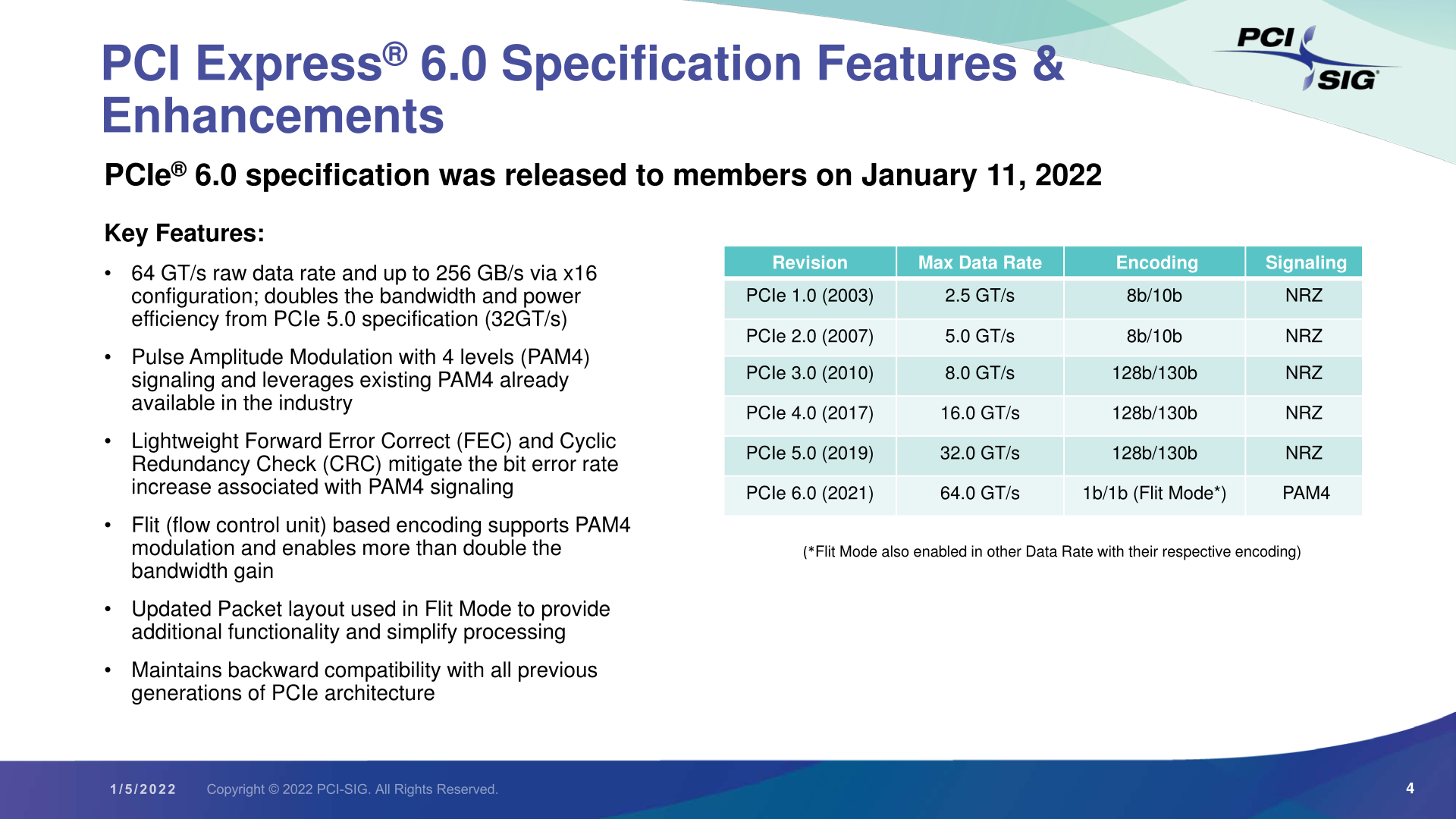

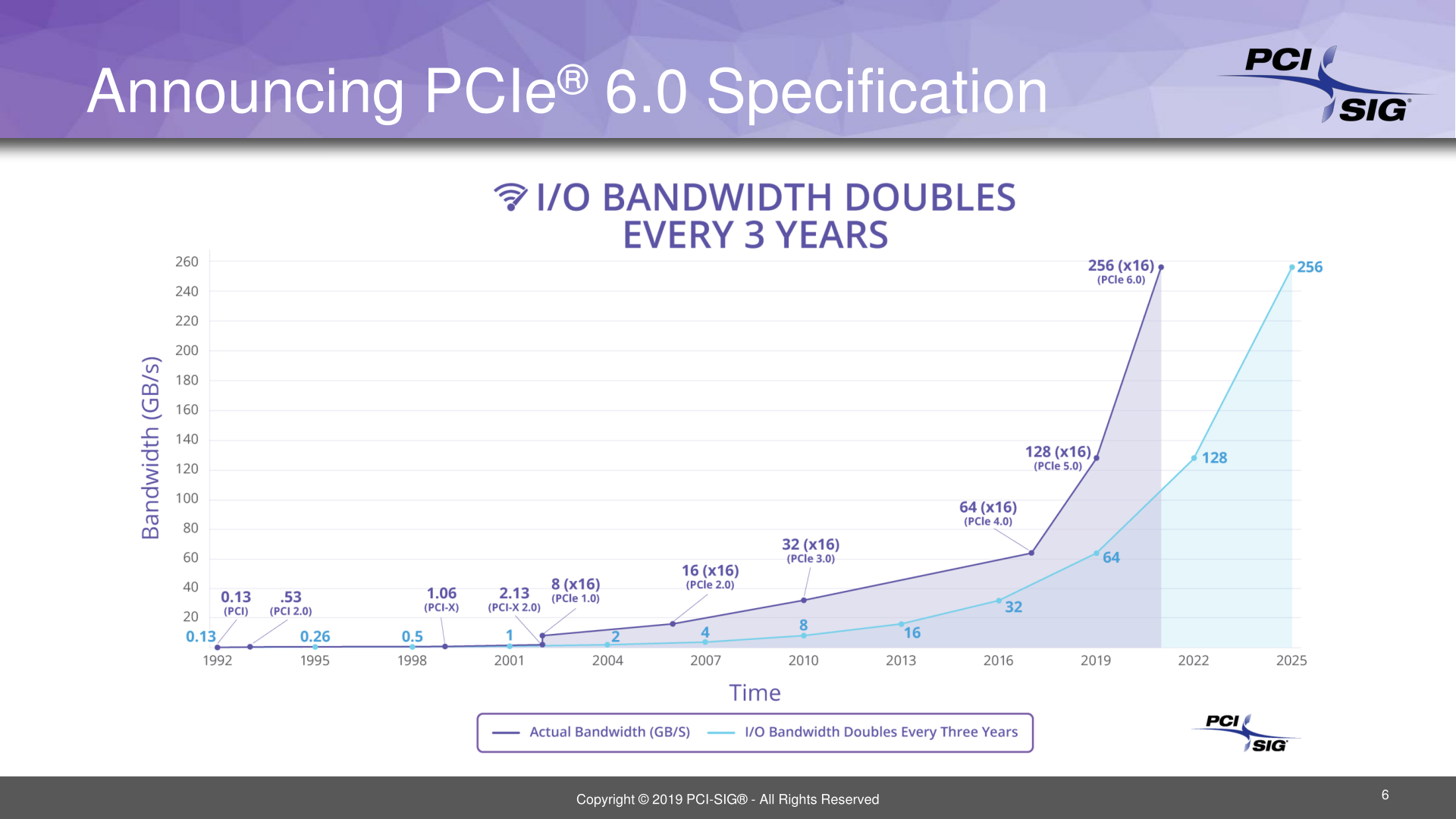

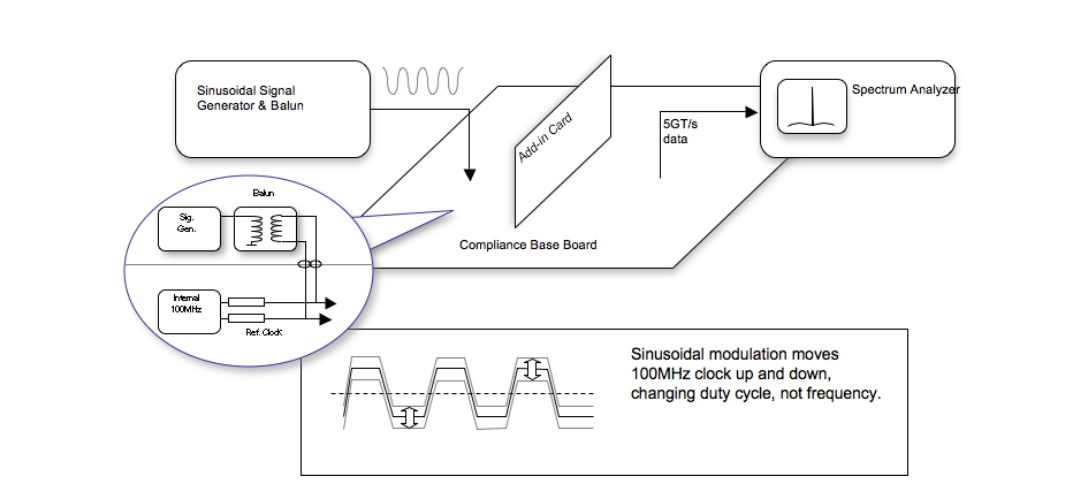

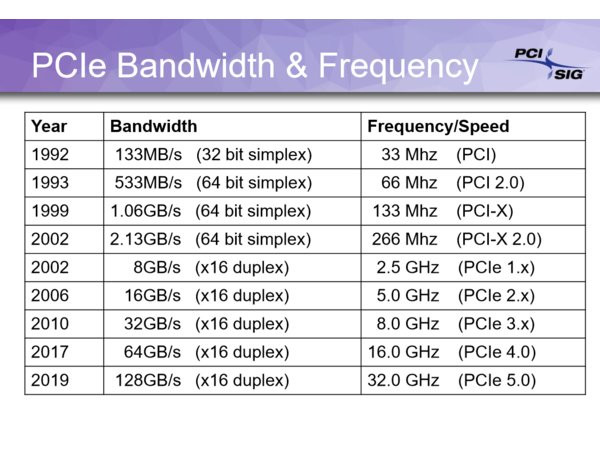

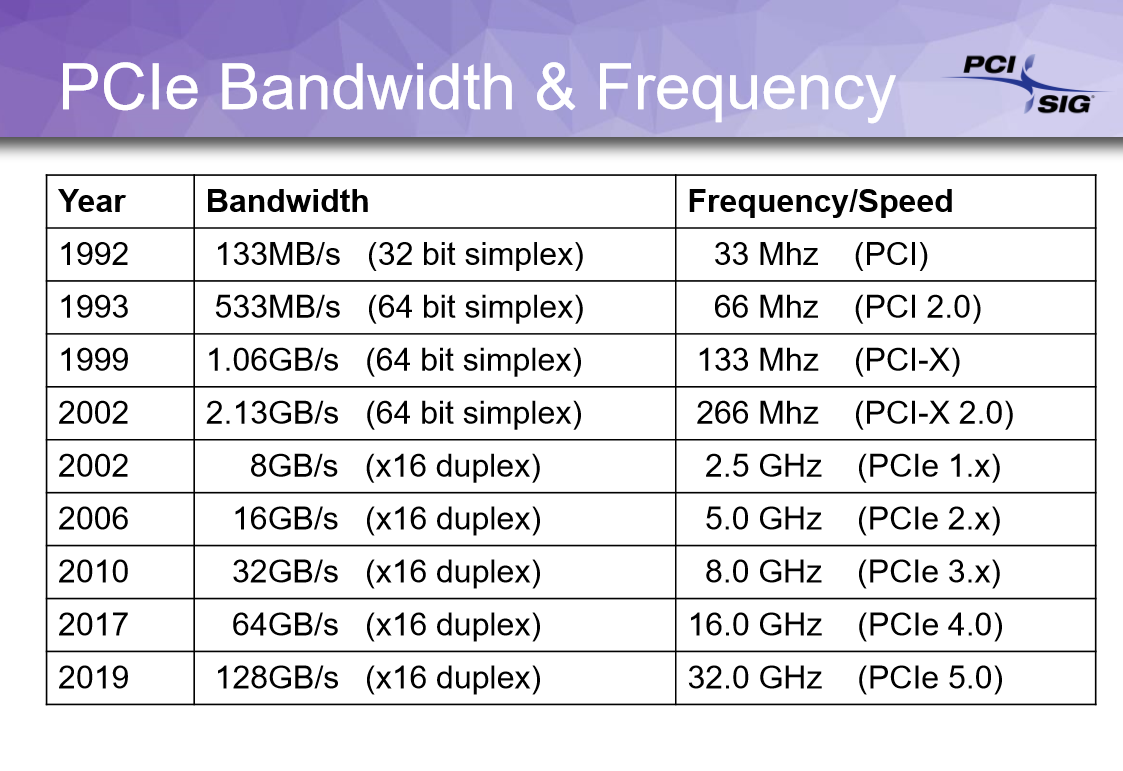

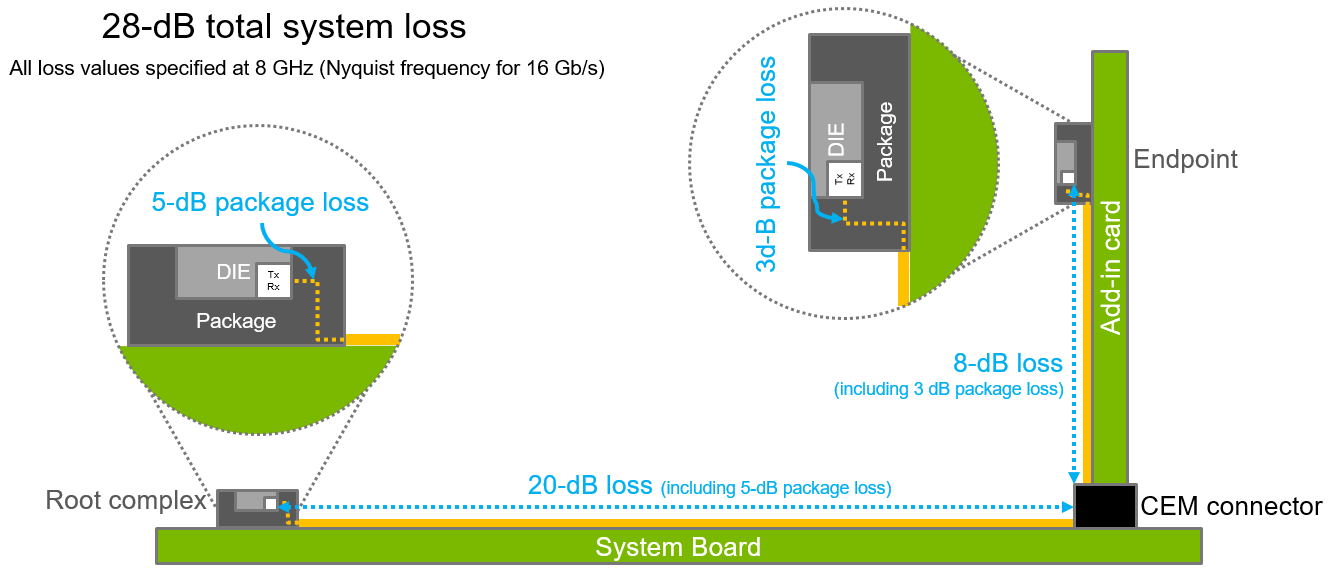

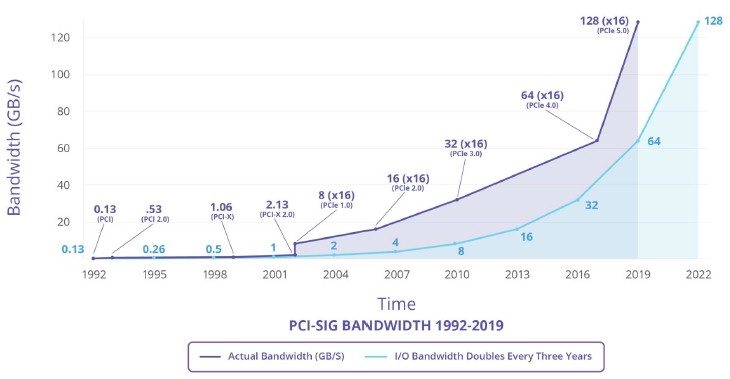

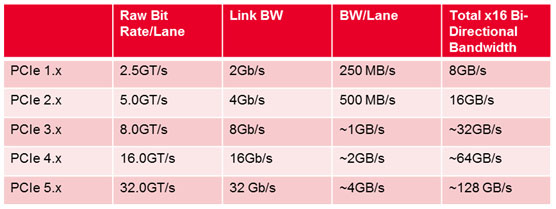

PCI Express Gen5 is Coming: What You Need to Know for Tx Measurements | 2019-02-19 | Signal Integrity Journal

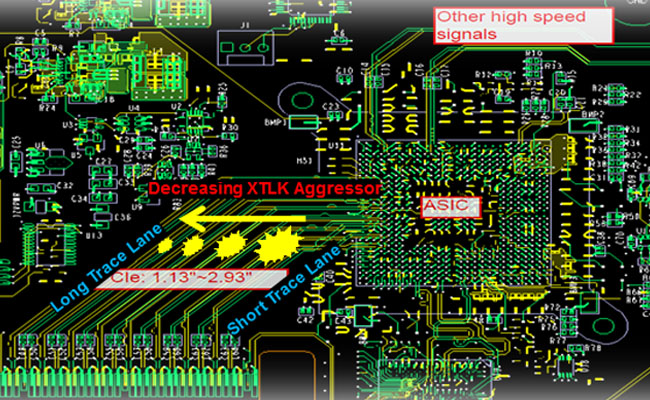

Timing is Everything: How to optimize clock distribution in PCIe applications - Analog - Technical articles - TI E2E support forums